4.8

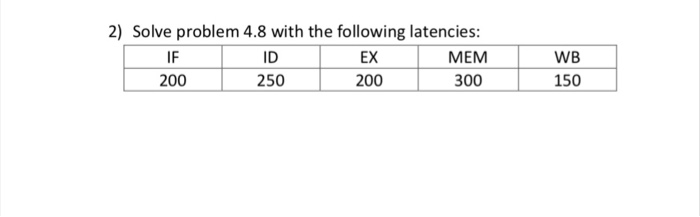

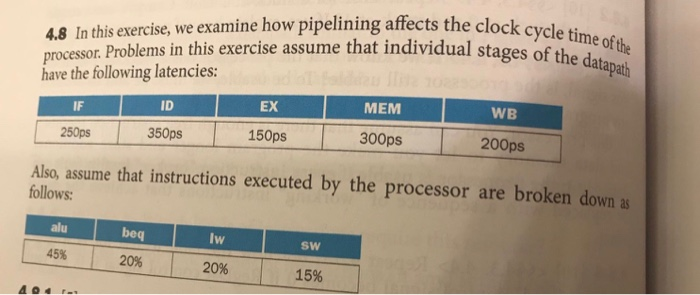

2) Solve problem 4.8 with the following latencies: WB 150 MEM EX 200 ID 250 IF 200 300 4.8 In this exercise, we examine how pipelining affects the clock cvdle t processor. Problems in this exercise assume that individual stages of the da have the following latencies: cycle time of the atapath WB MEM EX ID IF

2) Solve problem 4.8 with the following latencies: WB 150 MEM EX 200 ID 250 IF 200 300 4.8 In this exercise, we examine how pipelining affects the clock cvdle t processor. Problems in this exercise assume that individual stages of the da have the following latencies: cycle time of the atapath WB MEM EX ID IF

OR

OR