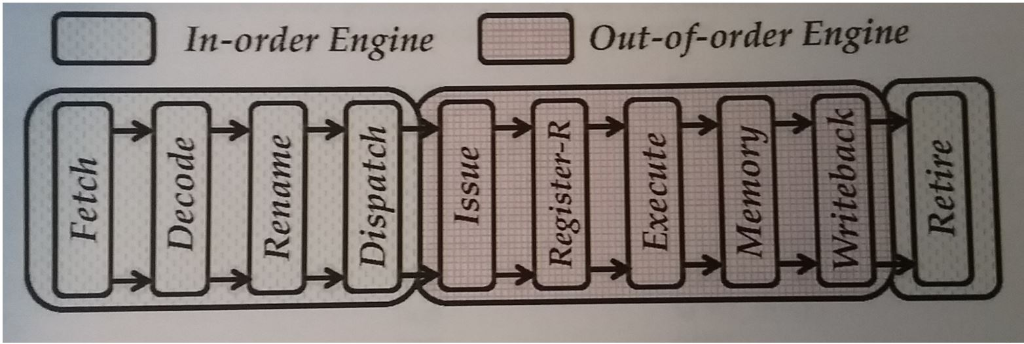

Consider and out of order pipeline as shown. There are 10 pipestages in this pipeline. The front-end –spanning from Fetch toDispatch—works in an in-order fashion (i.e., instructions arefetched, decoded, renamed and dispatched in program order). Thecore of the pipeline, from Issue to Writeback, works in anout-of-order fashion. Instructions are retired (committed) in anin-order fashion.

In this pipeline, an I-cache miss impacts the performancedifferently than a D-cache miss. This performance penaltydifference exists even when it takes equal number of cycles toservice the respective misses. Carefully explain why this isso.

Out-of-order Engine In-order Engine Show transcribed image

OR

OR