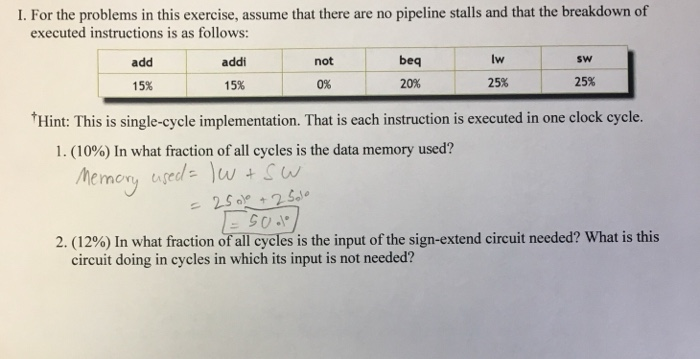

I. For the problems in this exercise, assume that there are no pipeline stalls and that the breakdown of executed instructions is as follows addi 15% Iw beq SW add not 25% 25% 0% 20% 15% Hint: This is single-cycle implementation. That is each instruction is executed in one clock cycle. I. (1096) In what fraction of all cycles is the data memory used? 2. (12%) In what fraction ofall cycles is the input of the sign-extend

I. For the problems in this exercise, assume that there are no pipeline stalls and that the breakdown of executed instructions is as follows addi 15% Iw beq SW add not 25% 25% 0% 20% 15% Hint: This is single-cycle implementation. That is each instruction is executed in one clock cycle. I. (1096) In what fraction of all cycles is the data memory used? 2. (12%) In what fraction ofall cycles is the input of the sign-extend

OR

OR