Text:

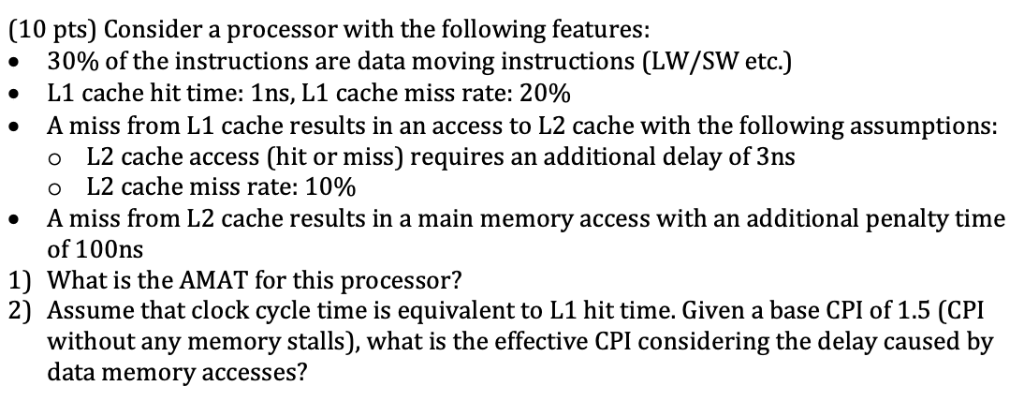

Consider a processor with the following features:

• 30% of the instructions are data moving instructions (LW/SWetc.)

• L1 cache hit time: 1ns, L1 cache miss rate: 20%

• A miss from L1 cache results in an access to L2 cache with thefollowing assumptions:

o L2 cache access (hit or miss) requires an additional delay of3ns

o L2 cache miss rate: 10%

• A miss from L2 cache results in a main memory access with anadditional penalty time of 100ns

1) What is the AMAT

OR

OR